PCB-I-Online

Native Board Import

Panel Optimizer

PCB-I-Physics

**PLM**

### **High Quality Stencil Preparation**

Schindler & Schill GmbH

Im Gewerbepark D33 93059 Regensburg

Germany

01/2023

Tel: +49 941 56813620 Email: info@easyLogix.de

Web: www.easyLogix.de

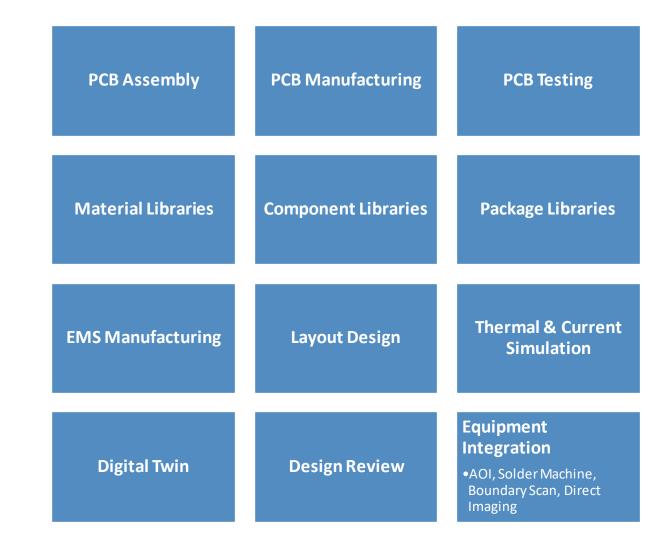

# **Product Categories**

# Advanced Stencil Preparation

#### **Increase in Efficiency and Productivity**

PCB-Investigator automates data preparation while allowing the flexibility customers needs. Takin care of all different types of stencils and components.

Standard Stencil design / Step-Stencil Technologies

Train your CAD System for best results

Use knowledge getting from components

Adding the experience from internal production

Set up a looped process to learn with each product

IPC-7525A

Stencil Design Guidelines

- Electroforming

- Laser Cutting

- Chemical Etching

- Stainless Steel SMT Stencils

- Mylar and Kapton SMT Stencils

One of the features of PCB-Investigator is its ability to handle all different types of stencils and components. This includes standard stencil design and step-stencil technologies, as well as stencils made using electroforming, laser cutting, chemical etching, and other techniques. PCB-Investigator can also support different types of stencil materials.

In addition to its automation capabilities, PCB-Investigator also offers flexibility to meet the specific needs of customers. This includes the ability to train the CAD system for optimal results, use knowledge gained from components and internal production experience, and set up a looped process to learn with each product. By using PCB-Investigator, customers can streamline their data preparation process and improve their efficiency and productivity in PCB manufacturing.

Reaction Generator

Reacti

Suitable for both standard and STEP stencils.

Switching from predefined to rule-based creation improves the automation process, making it more reliable and independent. This approach also puts the production technology in the forefront, ensuring that the process is tailored to the specific requirements of the application..

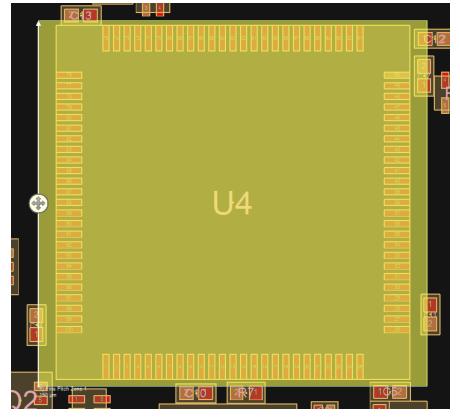

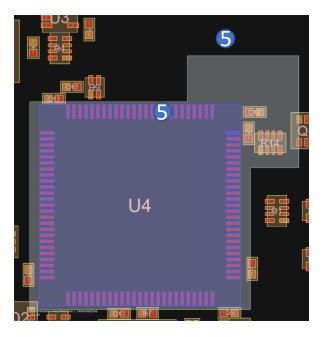

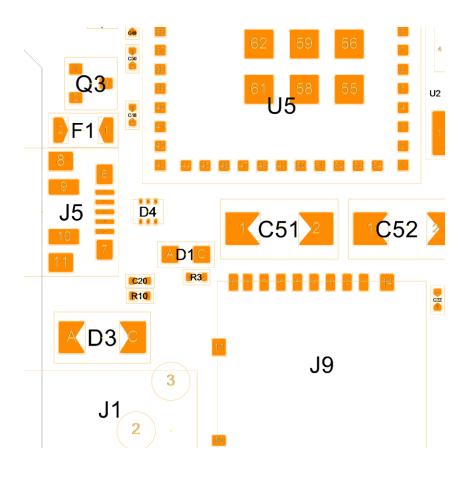

# Package Types

#### Assign the right optimization to each package

- QFN quad flat pack

- PQFN power quad flat-pack, no-leads, with exposed die-pad[s] for heat sinking.

- BGA ball grid array

- CGA column grid array

- CCGA ceramic column grid array

- BGA micro-BGA, with ball spacing less than 1mm.

- COB chip-on-board

- COF chip-on-flex

- COG chip-on-glass

- SOIC Small outline integrated circuit

- SOP Small outline package

- PLCC Plastic leaded chip carrier

- TSOP Thin small outline package

- SSOP Shrink small outline package

- TSSOP Thin shrink small outline package

- QSOP Quarter-size small outline package

- VSOP Very small outline package

- LQFP Low profile quad flat pack

- PQFP Plastic quad flat pack

- CQFP Ceramic quad flat pack

- TQFP Thin quad flat pack

- MLP Lead-frame package

- MQFP Metric Quad Flat Pack

- CSP Chip Scale Package

Using PCB-Investigator, customers can automate the stencil preparation process and streamline their PCB manufacturing workflow. The tool can help to ensure that the correct stencils are created for the package types being used, improving efficiency and reducing the risk of errors.

Advanced rule-based stencil generation taking component information into account

To create high-quality SMT pads for your stencil, the following steps should be taken:

- -Create all necessary patchwork and steps for your stencil

- -Use all relevant rules to create the SMT pads

- -Ensure that the stencil conforms to IPC standards

- -Set the overall thickness of the stencil to the appropriate level for the specific application.

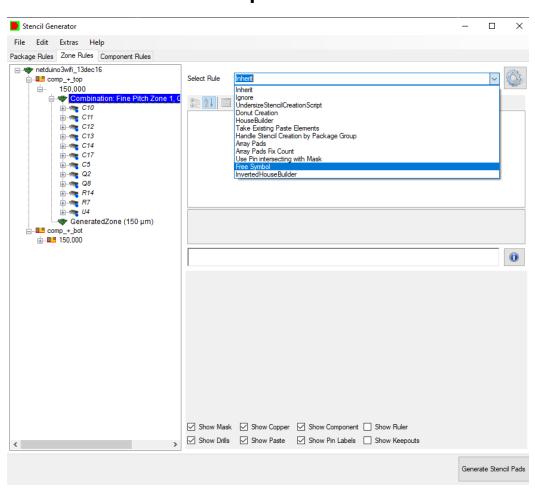

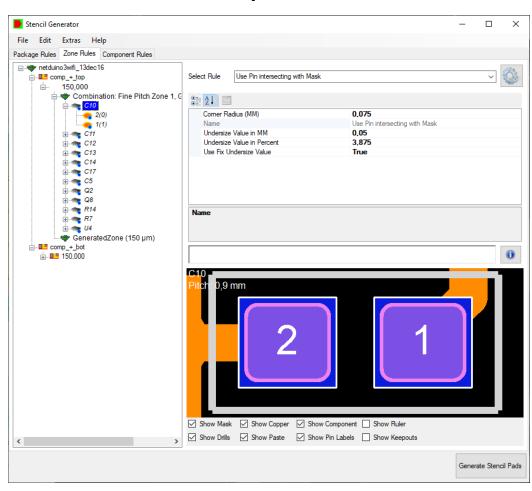

#### Advanced rule-based stencil generation taking component information into account

PCB-Investigator is used to create patch work and steps for stencils. PCBI can be configured to use a variety of rules to create high quality SMT pads, ensuring that the stencils produced meet industry standards and are suitable for use in PCB manufacturing.

In addition to creating the patch work and steps, PCB-Investigator can also be used to check the stencil against IPC (International Electrotechnical Commission) standards.

This can ensure that the stencil meets the necessary quality and performance requirements for your project.

PCB-Investigator can set the overall thickness of the stencil, ensuring that it is suitable for use with the particular manufacturing process and equipment being used. By using PCB-Investigator, customers can streamline their stencil preparation process and improve the efficiency and quality of their PCB manufacturing operations.

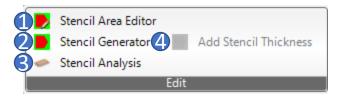

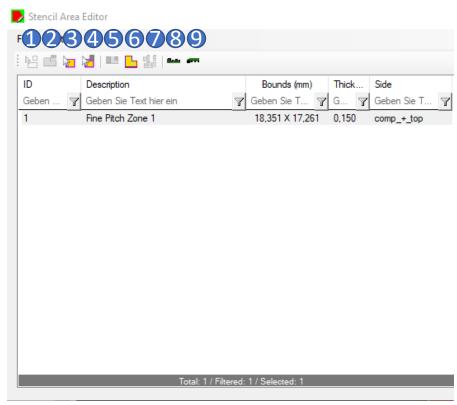

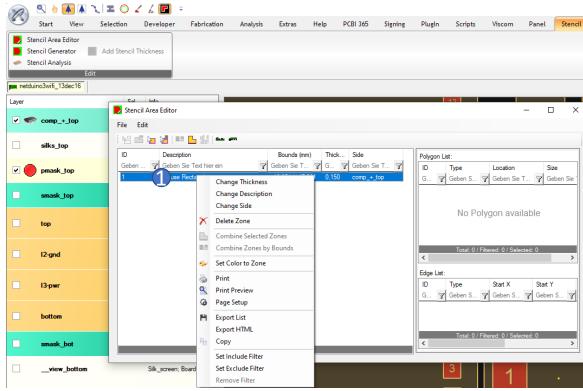

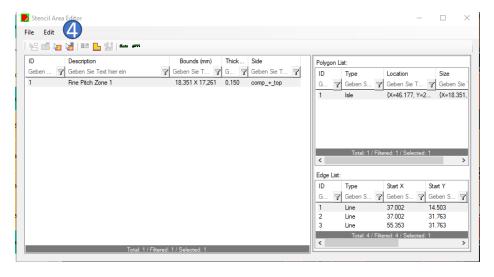

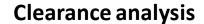

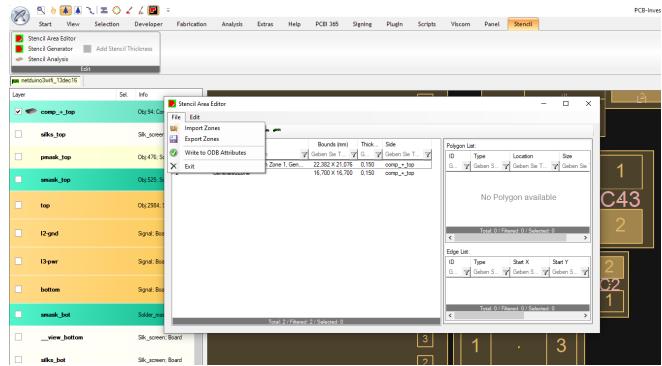

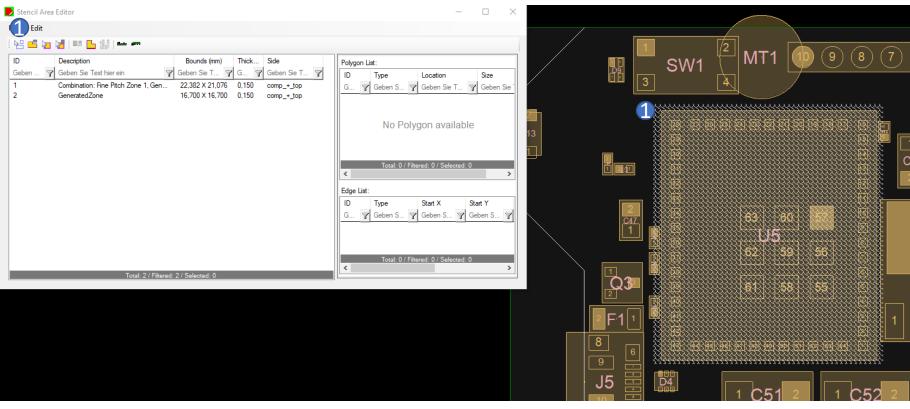

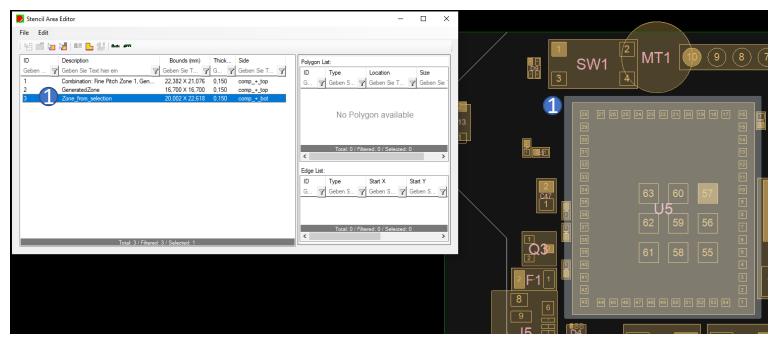

#### **Stencil Area Editor operations**

- 1. Add selection as zone

- 2. Set Area

- 3. Add zone by rectangle

- 4. Add zone by rectangle with cutouts

- 5. Combine selection

- 6. Add zone rectangle

- 7. Combine zones overlapping

- 8. Switch to Top View

- 9. Switch to Bot View

#### Edit base settings for each area

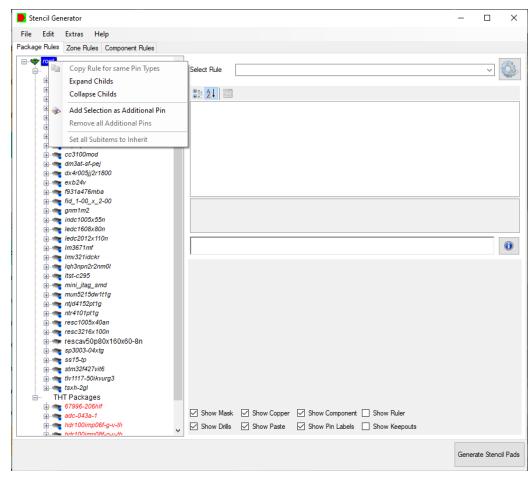

#### 1. Context menu

#### **Edit the shape**

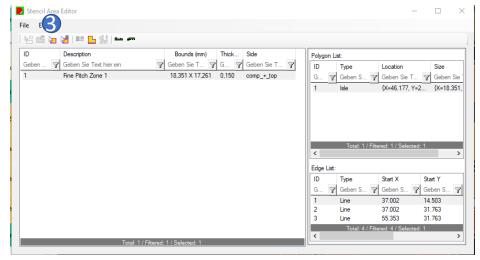

3. Add a new zone by drawing a rectangle Note: For high quality, it is recommended not to cut pin pads. You can combine areas e.g. from different parts to get ideal areas.

#### **Zone function**

4. Add a new zone with cutting out a previous zone by drawing a rectangle

#### **Zone function**

5. Combine different zones to one zone

#### Manage zone settings

Zone settings can be saved in ODB attributes, exported as xml and imported from xml.

#### Add zones by predefined drawings

- 1.Increased flexibility: A step stencil allows for different paste deposition levels in different areas, which can be useful for specific applications.

- 2.Improved accuracy: The different thickness levels in a step stencil can provide more precise and accurate paste transfer, as the aperture walls are closer to the pads in some areas.

- 3.Reduced paste bridging: The different thickness levels in a step stencil can reduce the risk of paste bridging between apertures, which can lead to better yields and improved overall quality of the soldered joints.

- 4.Reduced costs: A step stencil allows for more efficient use of paste, which can lead to reduced costs for the soldering process.

- 5.Increased process control: By adjusting the thickness of the stencil at different areas, it allows better control of the paste depositon, which can have a positive impact on the final product quality.

#### Add zones by predefined drawings

#### Add zones by predefined drawings

Improved accuracy: Smaller thickness stencils can provide more precise and accurate paste transfer, as the aperture walls are closer to the pads.

Better paste release: The thinner stencils can lead to better release of the paste from the apertures, resulting in more consistent and reliable paste deposition. Reduced paste bridging: Thinner stencils can reduce the risk of paste bridging between apertures, which can lead to better yields and improved overall quality of the soldered joints.

$Reduced\ costs: Thin\ stencils\ require\ less\ material, which\ can \ lead\ to\ reduced\ manufacturing\ costs.$

$Increased\ flexibility: Thin\ stencils\ can\ be\ more\ flexible, which\ can\ be\ useful\ in\ applications\ where\ the\ stencil\ needs\ to\ conform\ to\ irregular\ or\ curved\ surfaces.$

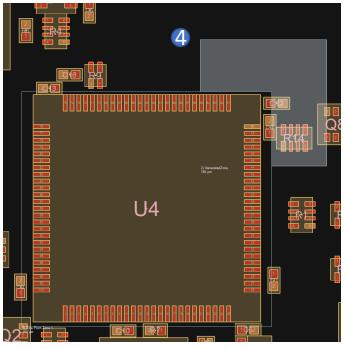

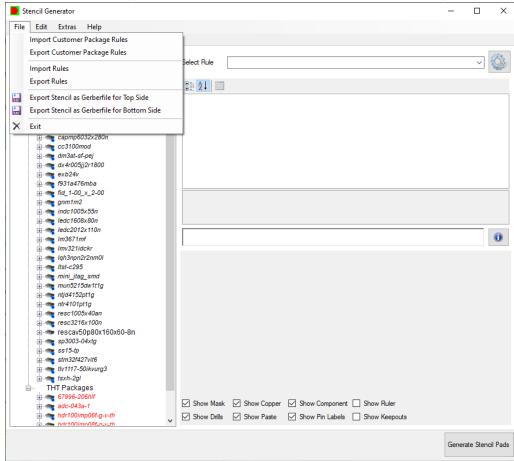

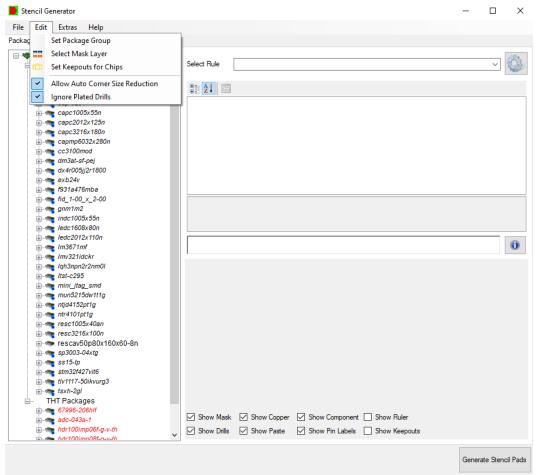

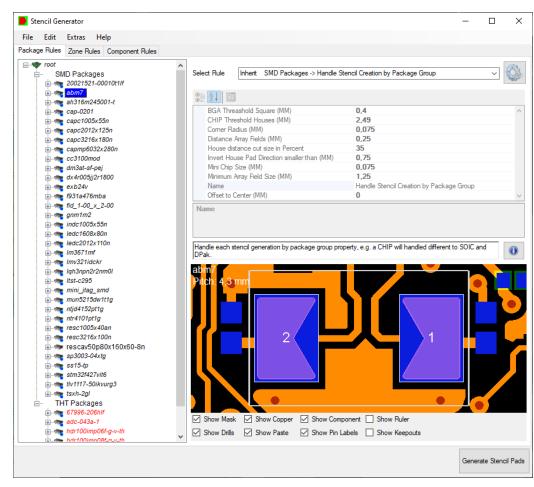

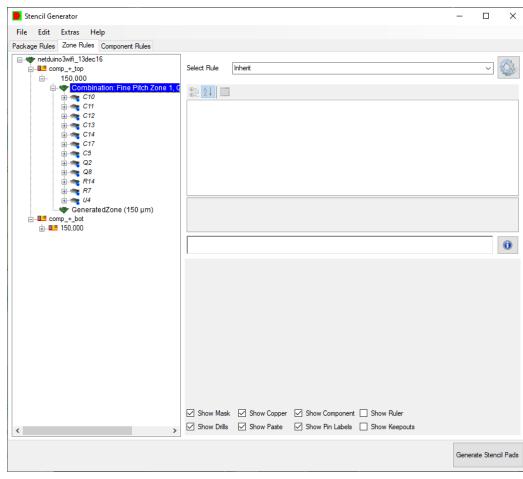

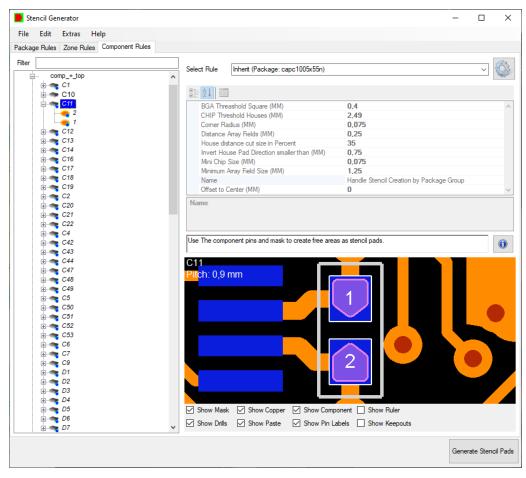

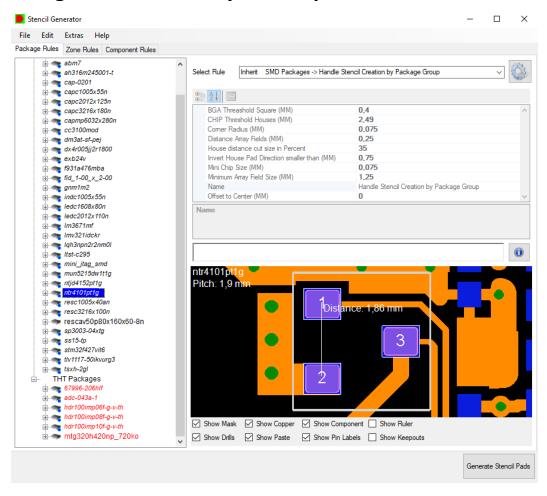

#### Main setup for paste pad creation

The Stencil Generator uses all zones defined by the Stencil Area Editor. If there are no zones the outline will be used as main zone.

Use default rules for your company.

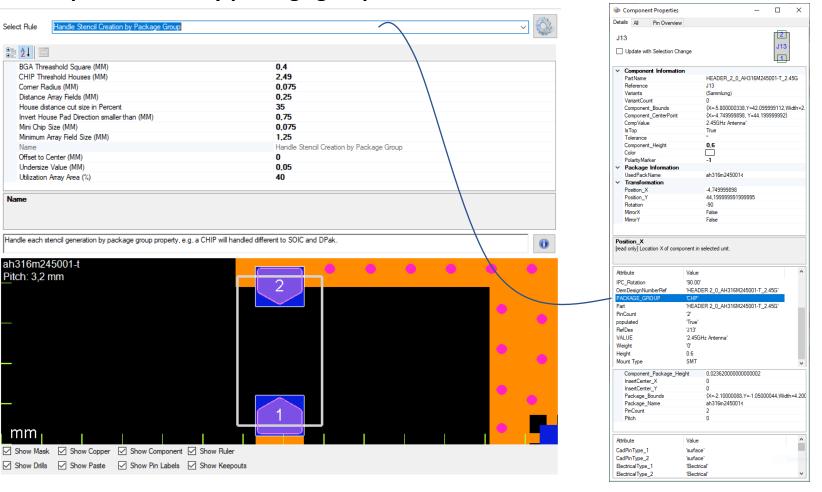

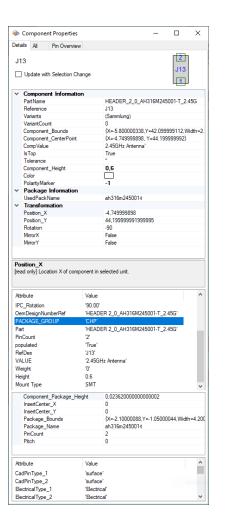

Setting a package group, enables the Wizard to set the rules regarding it. SOICs, Chips, BGAs and any definition needed.

The Wizard is delivered we predefined settings. To adjust all data preparation to your product you can setup own data preparation Scripts to adjust to your equipment.

#### **Build in automation support**

Set Package Group is only necessary if your data don't contain a proper information.

Customers with EPL ("Easylogix Part Library") can resolve trusted data from EPL.

The Wizard also process layouts with multiple mask layers in the stack-up.

Set "Keepouts for Chips" is only available if you have MPN packaged defined. It will handle the usable area for you.

You also can set plugged drills as free usable area.

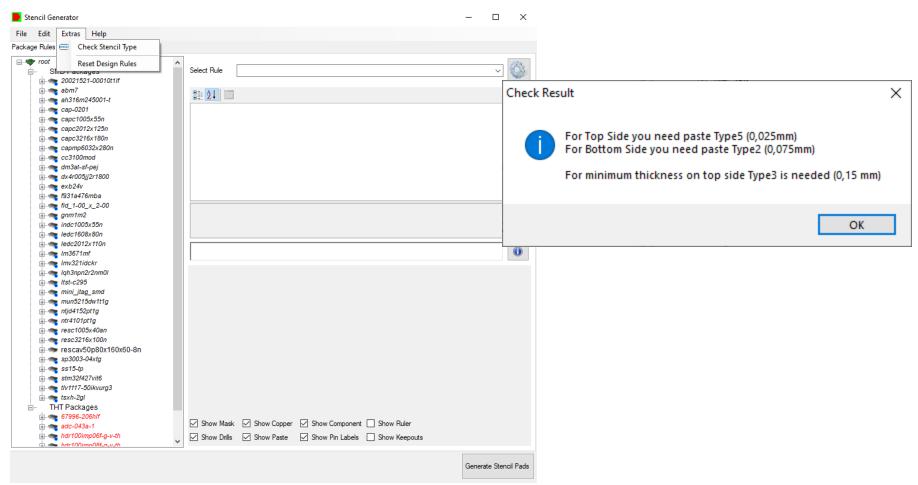

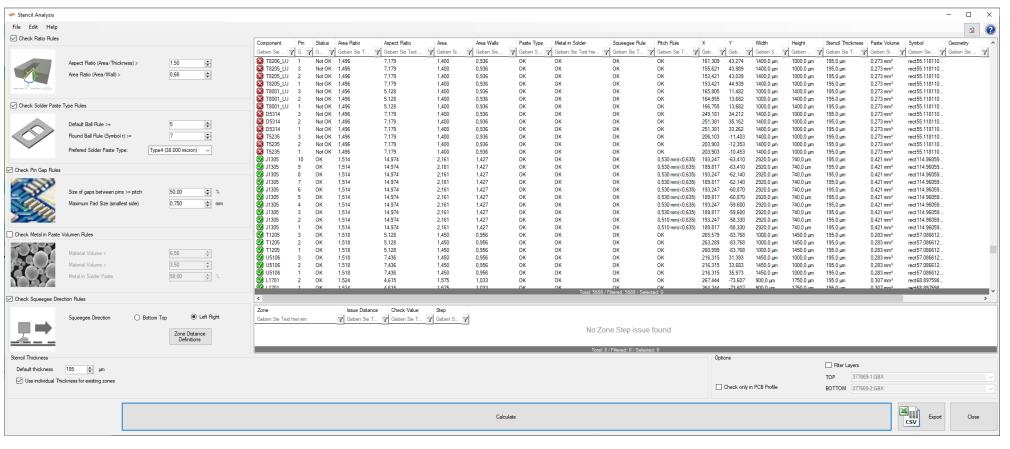

#### **Check stencil by using current rules**

#### Crate stencil pin by any drawing

#### **Rule preview**

#### Integrated measure system in preview

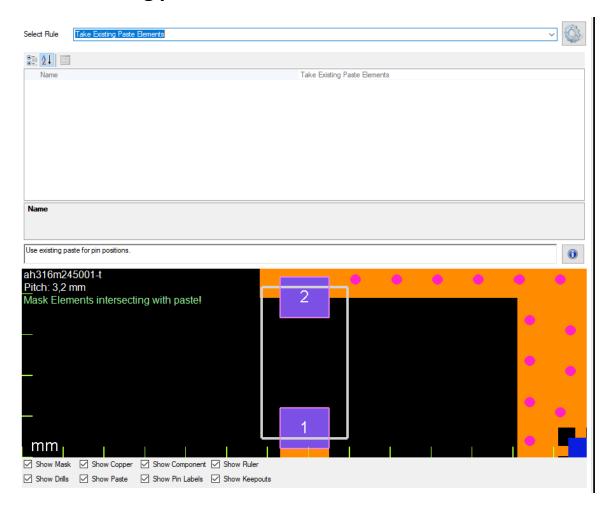

#### **Take existing paste elements**

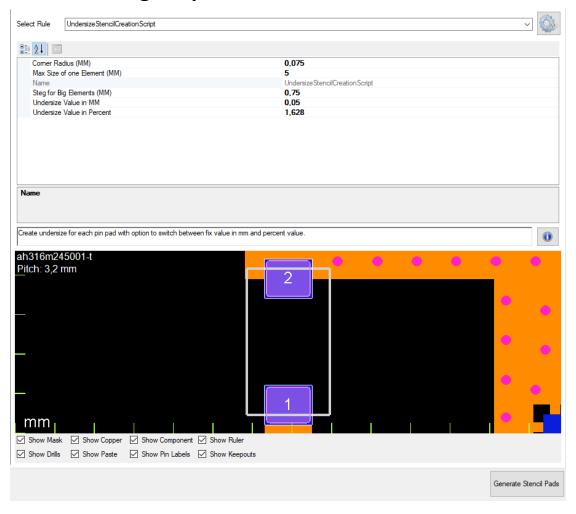

#### **Undersize original pads**

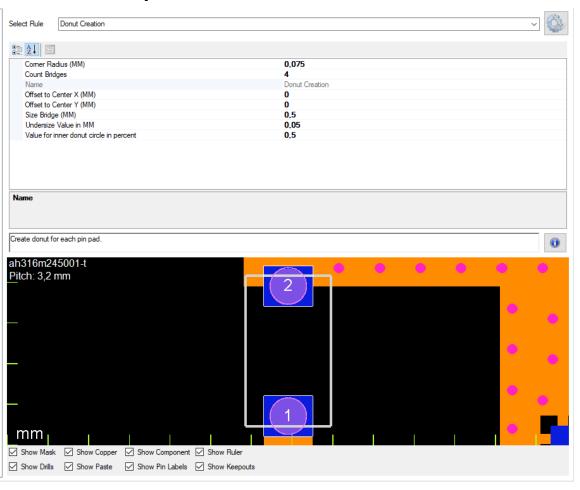

#### **Create donat pads**

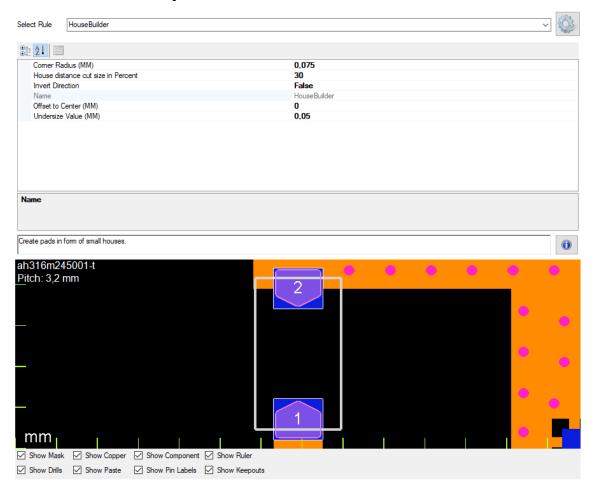

#### **Create house pads**

#### Handle pad creation by package group

#### Handle pad creation by package group

#### Predefined package groups

| "CONNECTOR_SMT":   |

|--------------------|

| "CONNECTOR THT":   |

| "FIDUCIAL_CIRCLE": |

| "FIDUCIAL RECT":   |

| _                  |

| "FIDUCIAL_CROSS":  |

| "FIDUCIAL":        |

| "LASER":           |

| "OTHER":           |

| "IGNORE":          |

| "DMC":             |

| "BBS":             |

| "NOT_PLACED":      |

| "CAE":             |

| "COIL":            |

| "CHP":             |

| "L CHP":           |

| <del>-</del>       |

| "R_CHP":           |

| "C_CHP":           |

| "F_CHP":           |

|                    |

|                    |

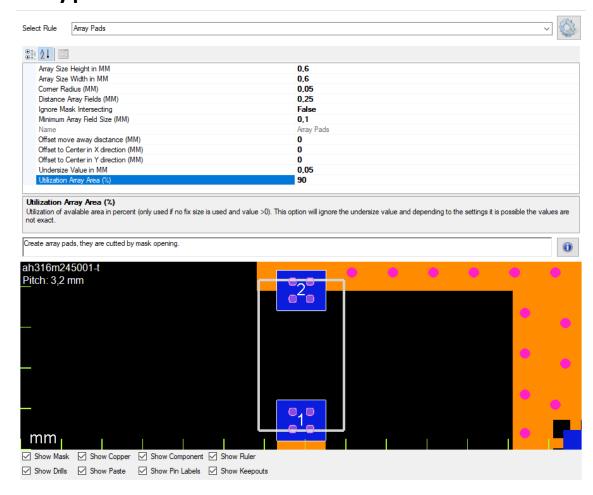

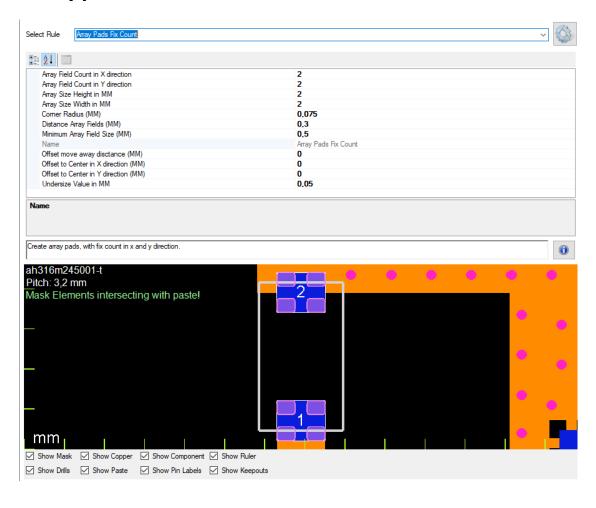

#### **Array pads**

#### Array pads fixed count

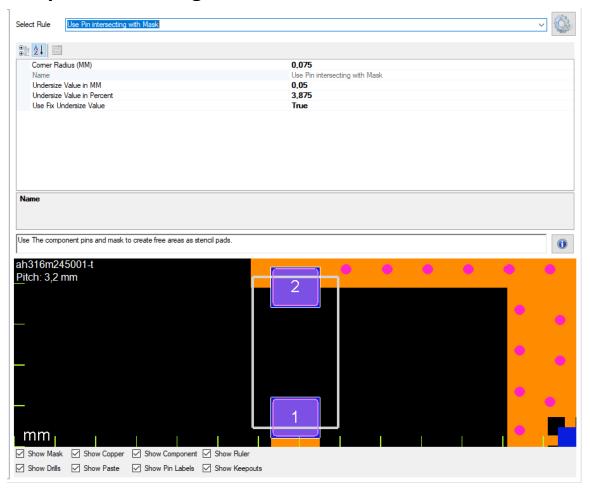

#### Use pin intersecting with solder mask

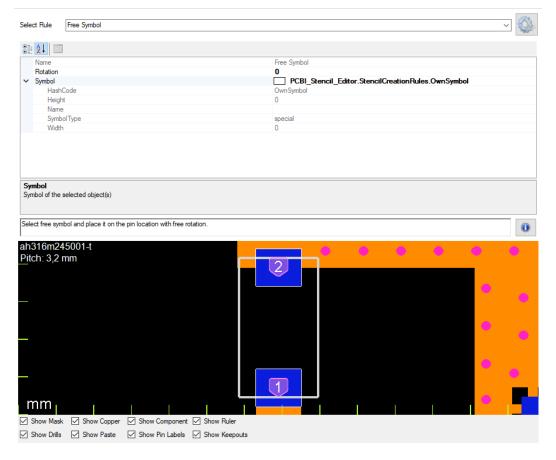

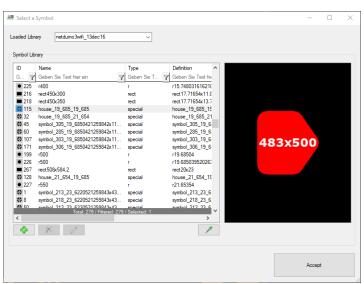

#### **Change symbol**

Insert symbols from job or from library

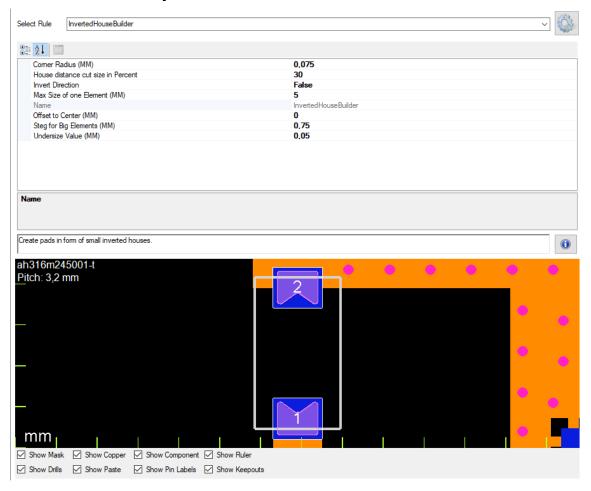

#### **Inverted house pad**

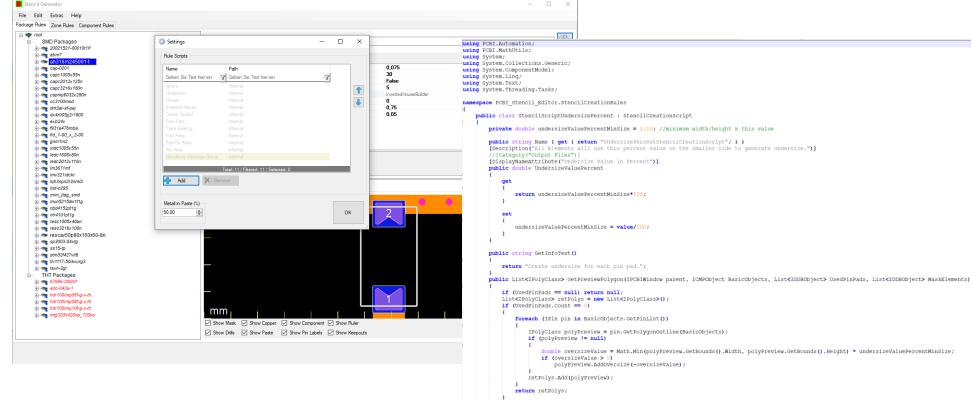

#### Add own rules to your stencil automation

Interface: StencilCreationScript

## Panel

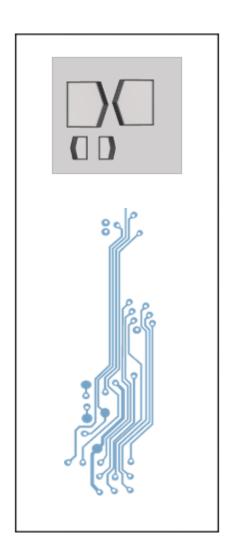

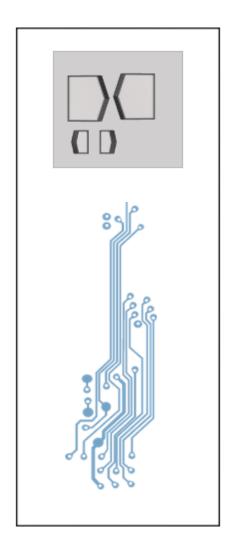

### Send the stencil data in your preferred format to your supplier

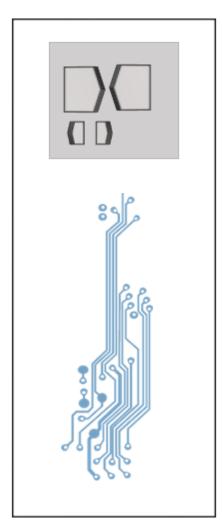

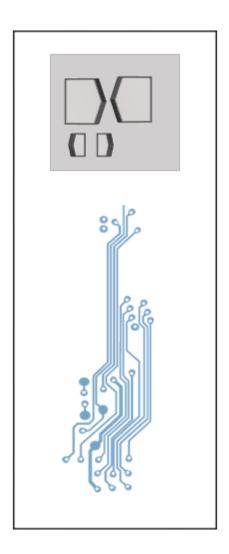

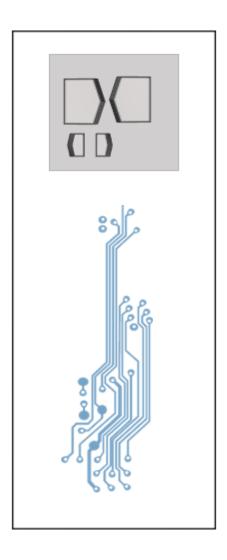

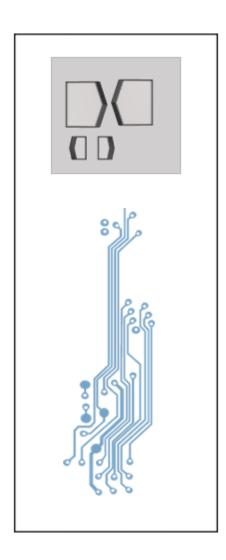

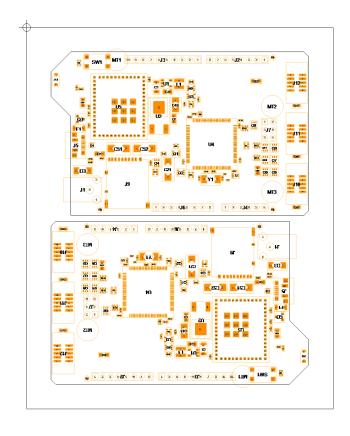

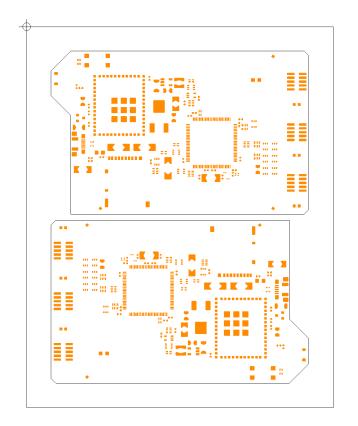

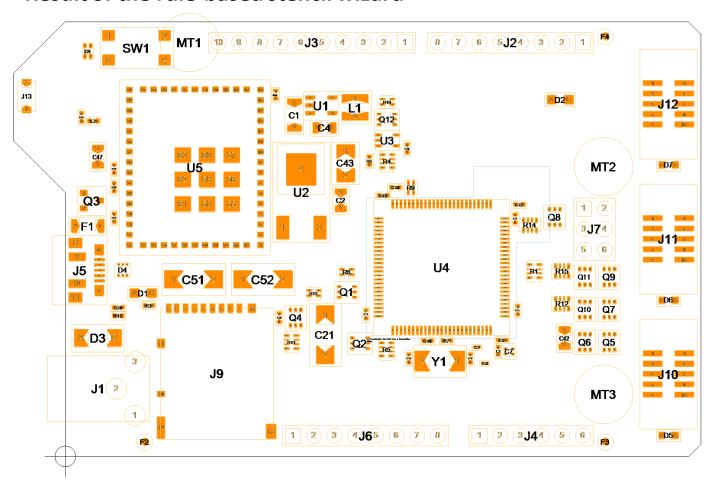

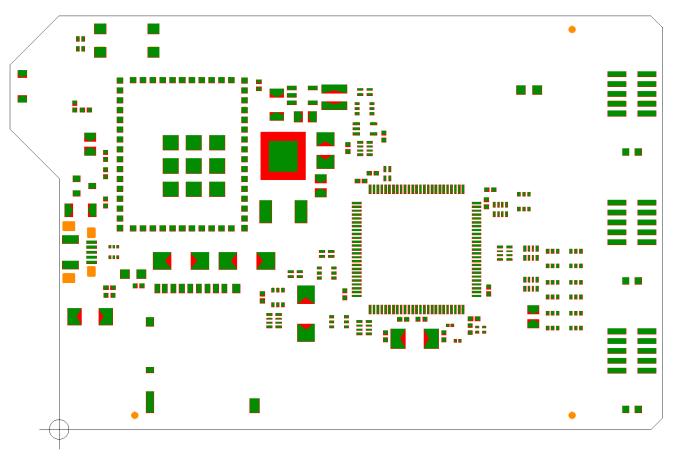

#### Result of the rule-based stencil wizard

#### Before and after

### **Stencil pad details**

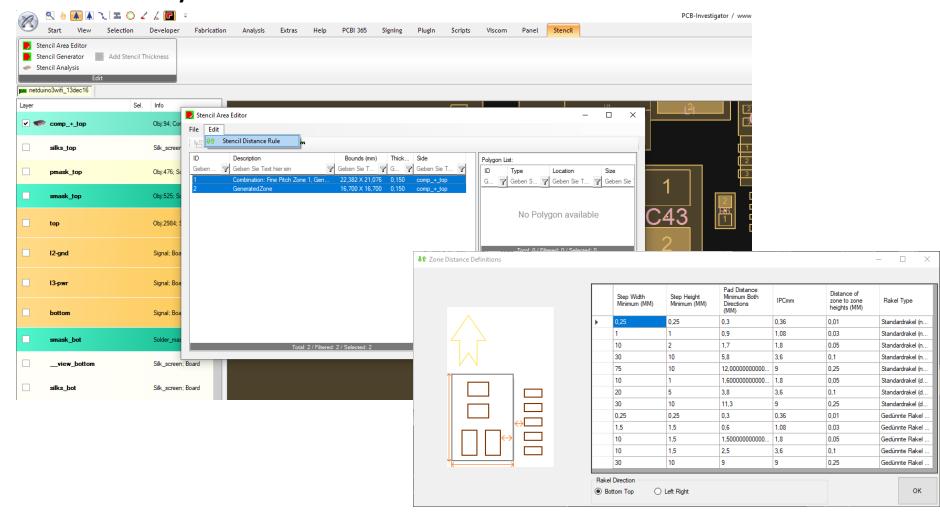

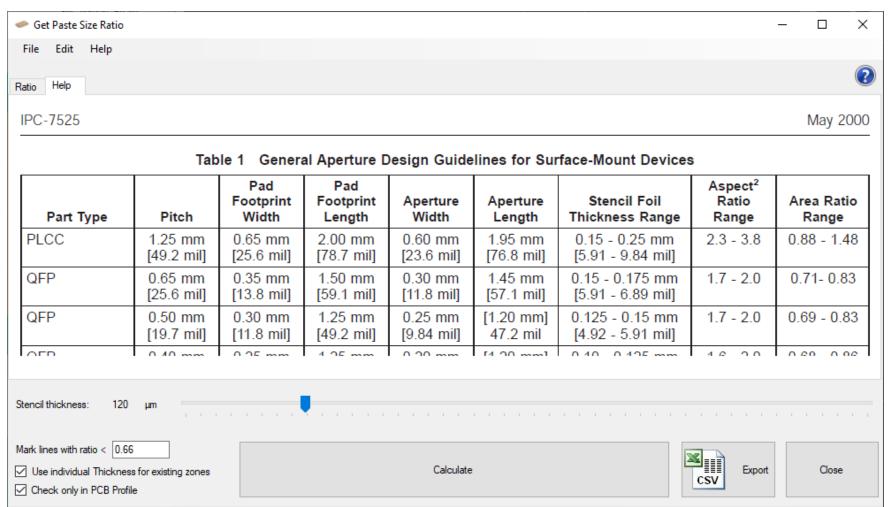

# Stencil Analyzer

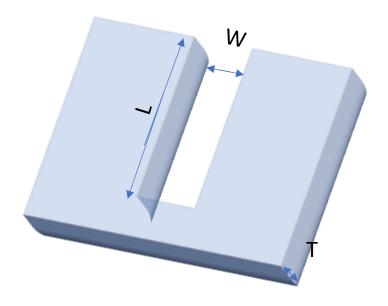

### Stencil Ratios

#### **Solder Paste Stencil Ratios**

In order to ensure efficient transfer of solder paste from a stencil aperture to a pad during the soldering process, there are two main ratios to consider:

•Aspect ratio: the relation between the width of narrowest aperture and the thickness of the stencil. This ratio should be at least 1.5.

•Area ratio: gives a more accurate and detailed indication of a stencil's paste release performance. This is the ratio between the area of the aperture and the area of the hole walls. This ratio should be at least 0.66.

Aspect Ratio = W / T

Area Ratio = A (Pad) / A (Wall)

# Stencil analyzer

### Stencil Wizard

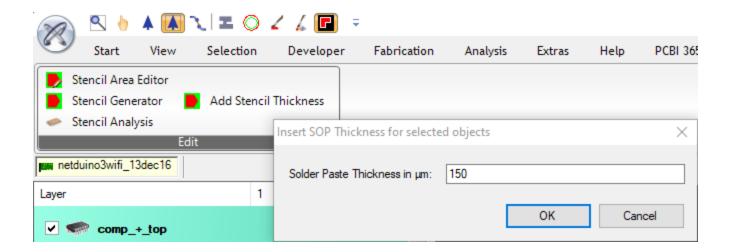

#### **Global stencil thickness**

You can set the thickness in the ODB++ attribute, the value is used in the SPI exports e.g. by Viscom to set different values for the paste thickness.

Note: If you do not save the zone values in the ODB attribute, they will not be recognized during export.

### Request Customized Functions

Get in touch,

<a href="mailto:info@easylogix.de">info@easylogix.de</a>

Guenther Schindler

Tel. +49 941 568 136 26

#### Useful Links:

PCB-Investigator www.pcb-investigator.com

PCBi-Physics www.PCBi-Physics.com

Native Board Import (3D Interface to CATIA, SiemensNX, SolidWorks, SolidEdge) www.sts-development.biz

GerberLogix www.gerberLogix.com

Online Gerber Viewer www.Gerber-Viewer.com

Software Development, CAD Converter, data connection  $\underline{www.easyLogix.de}$

In conclusion, PCB-Investigator is a powerful and versatile tool that can streamline the PCB design and manufacturing process. It offers a wide range of features and capabilities that can help to improve efficiency, reduce costs, and ensure the highest quality of your final product. Whether you are a designer, manufacturer, or engineer, PCB-Investigator is an essential tool for any professional working in the PCB industry. With its ability to automate and streamline various processes, it can help you to achieve your goals and stay ahead of the competition.

04/10/2018 49